All system/360 functional characteristics having programming significance are completely and concisely described.

The description, which is formal rather than verbal, is accomplished by a set of programs, interacting through common variables, used in conjunction with auxiliary tables.

The language used in the programs involves operators and notation selected from mathematics and logic, together with additional operators and conventions defined to facilitate system description.

Although the formal description is complete and self-contained, text is provided as an aid to initial study.

Examples to illustrate the application of the formal description are given in an appendix.

## A formal description of SYSTEM/360

by A. D. Falkoff, K. E. Iverson, and E. H. Sussenguth

This paper presents a precise formal description of a complete computer system, the IBM SYSTEM/360. The description is functional: it describes the behavior of the machine as seen by the programmer, irrespective of any particular physical implemention, and expressly specifies the state of every register or facility accessible to the programmer for every moment of system operation at which this information is actually available.

The work is based on the system/360 manual<sup>1</sup> and on interpretations and revisions furnished by the system architects, some of whom have assisted in a thorough audit of the present description.<sup>2</sup>

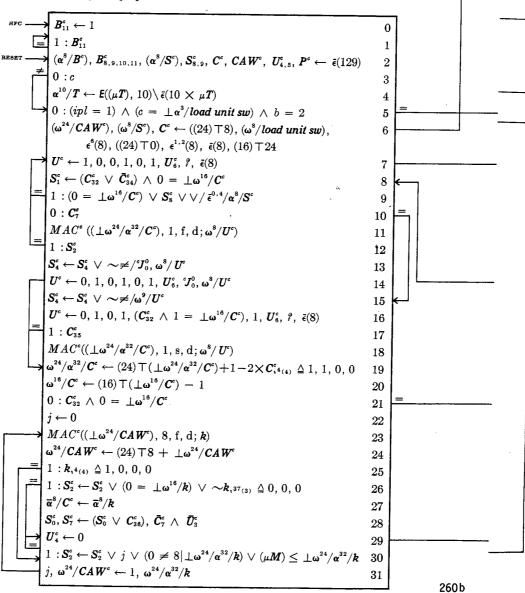

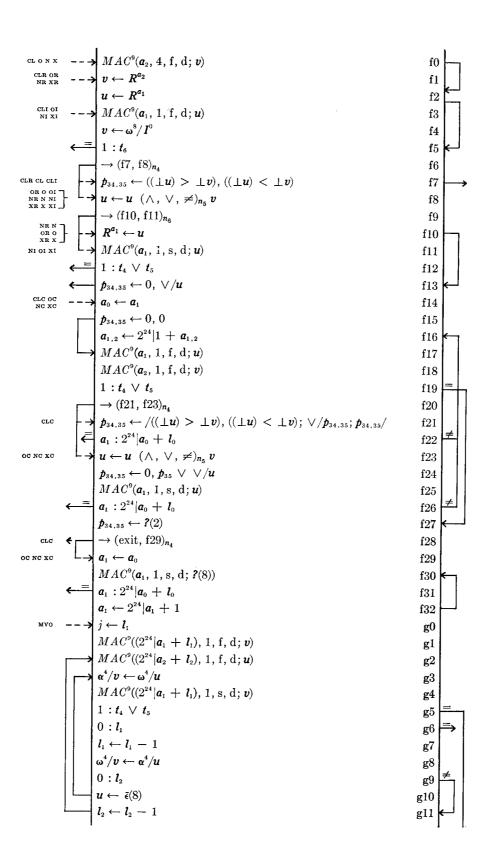

The formal description comprises a set of programs and auxiliary tables, all of which are grouped for easy cross-reference beginning on page 240.<sup>2</sup> These provide a complete, self-contained description of the system which, after some familiarity with the notation and programs is gained, will be found more convenient for reference than verbal description. An appendix furnishes examples of reference use of the material. The remainder of the text is designed primarily as a guide and aid in the initial reading of the programs.

The second and third sections describe the central processing unit and the input/output system, respectively. The first section defines the notation employed and illustrates its use. Further illustrations may be found in the references 4, 5, 6.

### The notation

A system is described by a collection of interacting programs, each program consisting of a list of statements executed in an alterable, but specified, sequence. The interaction between programs occurs through shared variables and through direct alteration of the sequence in one program by another.

Statements are of two major types, called specification and branch. A specification statement incorporates a left-pointing arrow and implies that its execution respecifies the value of the variable to the left of the arrow by the value of the expression to the right of the arrow. Thus, if x and y have values 3 and 4, respectively, the execution of the specification statement

$$z \leftarrow x + y$$

sets the variable z to the value 7.

The statements of a program are numbered serially from zero and are executed in serial order except that the execution of a branch statement may interrupt the sequence. One type of branch has the form

$$\rightarrow \alpha$$

, n

and implies that Program  $\alpha$  immediately executes its statement numbered n (to be referred to hereafter as line n) and proceeds from there. If the foregoing branch statement occurs in Program  $\beta$ (where  $\beta \neq \alpha$ ), the sequence in Program  $\beta$  is not affected. For example, the execution of line 1 of IPL, the initial program load program (page 259) resets CPU, the central processing unit program, to its line 0 but does not affect the sequence in IPL, which continues to line 2.

In the more familiar case the branch statement  $\rightarrow \alpha$ , n occurs in Program  $\alpha$ , and the program name is elided to yield the form  $\rightarrow n$ . Line 11 of the CPU program furnishes an example, causing a branch to one of lines 12, 14, 13, 17, or 19 according to which component of the vector (12, 14, 13, 17, 19) is selected by the index  $n_2$ . The statement itself completely specifies the branch, and the broken arrows from line 11 to each of its potential successors are provided merely as a graphic aid to comprehension.

Solid arrows from line to line are, however, used as an alternative specification of branching within a given program. An unlabelled arrow denotes an unconditional branch; thus line 12 of the CPU program is invariably followed by line 16. A solid arrow labelled with a relation R and emanating from a line containing a statement of the form

#### x:y

implies that the branch arrow is followed if and only if the relation  $x \Re y$  holds. Thus line 40 of the CPU is followed by line 1 if  $p_{14} = 0$ , and by line 25 if  $p_{14} \neq 0$ . In following branch arrows that cross, the path does not change direction at a crossing.

199

|                       | 1 Notation                                                                                                                    |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Operation                                                                                                                     | Notation (1)                                                                                                                                                                                                                                                                                      | Definition <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NDS                   | Scalar<br>Vector                                                                                                              | x<br>x                                                                                                                                                                                                                                                                                            | $x \equiv x_0, x_1, \dots, x_{(\nu x)-1}$ $\nu x \equiv \text{number of components}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OPERANDS              | Matrix                                                                                                                        | X                                                                                                                                                                                                                                                                                                 | $X \equiv \begin{bmatrix} X_0^0 & \cdots & X_{(\nu,X)-1}^0 \\ \vdots & \vdots & \vdots \\ X_0^{(\mu,X)-1} & \cdots & X_{(\nu,X)-1}^{(\mu,X)-1} \end{bmatrix} \begin{cases} X^i \equiv i \text{th row vector} \\ X_j \equiv j \text{th column vector} \\ \mu X \equiv \text{number of rows} \\ \nu X \equiv \text{number of columns} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                               |

| LOGICAL and NUMERICAL | Arithmetic  Absolute value Floor Ceiling Residue modulo $m$ And Or                                                            | $+ - \times \div$ $z \leftarrow \mid x$ $k \leftarrow \mid x$ $k \leftarrow \mid x$ $k \leftarrow m \mid n$ $w \leftarrow u \wedge v$ $w \leftarrow u \vee v$                                                                                                                                     | Usual definitions $z = \text{maximum of } x \text{ and } -x$ $k \le x < k + 1$ $k - 1 < x \le k$ $n = (m \times q) + k,$ $0 \le k < m$ $\begin{cases} u = 1 \text{ and } v = 1 \\ u = 1 \text{ or } v = 1 \end{cases}$ All operations are extended component-by-component to dimensionally compatible vectors and matrices. If one of the operands is a scalar, it is treated as a vector or matrix of appropriate dimension whose components are all equal. Examples: $z \leftarrow x + y$                                                                                                                                                                                                                                                                    |

| LOGIC                 | $egin{array}{ll} 	ext{Negation} & \left\{  ight. \end{array}$ Relation                                                        | $w \leftarrow \bar{u}$ $w \leftarrow \sim u$ $w \leftarrow x \Re y$                                                                                                                                                                                                                               | $ \begin{cases} w = 1 & \text{if } \\ u = 0 \\ x + x + y \\ w \leftarrow u \wedge v \\ w \leftarrow x \neq y \\ w \leftarrow x < y \end{cases} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REDUCTION             | Reduction<br>Row reduction<br>Column reduction<br>Matrix product                                                              | $z \leftarrow \bigcirc/X$ $z \leftarrow \bigcirc/X$ $z \leftarrow \bigcirc//X$ $z \leftarrow \bigcirc//X$ $Z \leftarrow X \stackrel{\circ}{\circ}, Y$                                                                                                                                             | $ z = x_0 \odot x_1 \odot \cdots \odot x_{(\nu x)-1} $ $\odot$ is any binary operator or relation. The case $X \stackrel{\star}{\sim} Y$ is the ordinary matrix product. The expressions $X \stackrel{\circ}{\circ}_{1} Y$ , and $x \stackrel{\circ}{\circ}_{1} Y$ are treated as in matrix algebra. Thus $x \stackrel{\star}{\sim} y$ is the scalar product.                                                                                                                                                                                                                                                                                                                                                                                                  |

| BASE VALUE            | Base 10 value Base 2 value { Representation base 10                                                                           | $z \leftarrow 10 \perp x$ $z \leftarrow \perp u$ $z \leftarrow \perp U$ $z \leftarrow \perp U$                                                                                                                                                                                                    | z is the base-10 value of the vector $x$ z is the base-2 value of the vector $u$ $z_i \equiv \perp U^i$ $pz \equiv n \text{ and } 10 \perp z \equiv 10^n \mid j$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SELECTION             | base 2  Catenation Row catenation Compression vector row column row list Row list expansion  Mask  Indexing  { Maximum prefix | $u \leftarrow (n)     j$ $z \leftarrow x, y$ $Z \leftarrow x \oplus y$ $z \leftarrow u/x$ $Z \leftarrow u/X$ $Z \leftarrow u//X$ $z \leftarrow E/X$ $X \leftarrow E(m, n) \setminus z$ $z \leftarrow /x; u; y/z$ $z \leftarrow x_m$ $z \leftarrow X^m$ $z \leftarrow X_m$ $w \leftarrow \alpha/u$ | $\begin{array}{l} \nu u \equiv n \text{ and } \underline{\qquad} u \equiv 2^n \mid j \\ \\ z \equiv x_0, x_1, \cdots, x_{(\nu X)-1}, y_0, y_1, \cdots, y_{(\nu y)-1} \\ Z_0 \equiv x; Z_1 \equiv y \\ \\ z \text{ obtained by suppressing from } x \text{ each } x_i \text{ for which } u_i \equiv 0 \\ Z' \equiv u/X; \\ Z_j \equiv u/X; \\ z \equiv X^0, X^1, \cdots, X^{(\mu X)-1} \\ \mu X \equiv m, \nu X \equiv n, \text{ and } E/X \equiv z. \text{ Thus } X \equiv \begin{bmatrix} z_0 & \cdots & z_{n-1} \\ z_n & \cdots & \cdots \\ \vdots & \vdots & \vdots & \vdots \\ x_i \equiv z_{m_i} \\ Z_i \equiv X^m; \\ Z_i \equiv X_{m_i} \\ w \equiv \alpha^{i}(\nu u) \text{ and } j \text{ is maximum for which } \wedge /w/u \equiv 1 \\ \end{array}$ |

| SHIFTING              | Left rotation<br>Right rotation<br>Left shift<br>Right shift                                                                  | $z \leftarrow k \uparrow x$ $z \leftarrow k \downarrow x$ $z \leftarrow k \uparrow x$ $z \leftarrow k \uparrow x$ $z \leftarrow k \downarrow x$                                                                                                                                                   | $ \begin{aligned} z_i &= x_i; j = (\nu x) \mid i + k \\ z_i &= x_i; j = (\nu x) \mid i - k \end{aligned}                                $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPECIAL VECTORS       | Full Characteristic Prefix Suffix Random  { Interval                                                                          | $w \leftarrow \epsilon(n)$ $w \leftarrow \epsilon^{i}(n)$ $w \leftarrow \alpha^{i}(n)$ $w \leftarrow \omega^{i}(n)$ $w \leftarrow ?$ $w \leftarrow ?(n)$ $w \leftarrow ?^{i}(n)$ $z \leftarrow v^{i}(n)$                                                                                          | $\begin{array}{l} w_i \equiv 1 \\ w_i \equiv ( \vee / i = j ) \\ w_i \equiv ( i < j ) \\ w_i \equiv ( (n-i) \leq j ) \\ w \equiv 0 \text{ or } 1 \text{ (arbitrary)} \\ w_i \equiv 0 \text{ or } 1 \text{ but } +/w \equiv j \\ z \equiv j, j+1, \cdots, j+n-1 \end{array}$ Dimension of $\boldsymbol{w}$ is $n$ . The $n$ may be omitted if it is clear from context.                                                                                                                                                                                                                                                                                                                                                                                         |

- ① The notation for each operation is only the portion to the right of the specification arrow; the variable to the left facilitates definition.

- ② Throughout this paper elementary operations occurring in compound expressions are, except as indicated by parentheses, executed in strict order from right to left. In this table the symbol ≡ is used instead of = to denote equality, since the latter denotes an operator of the class

- 3 The following arguments are used in the examples:

```

a \equiv 7, -6, 5, -4, 3

T0 1 2 3 47

b \equiv 3, 2, 1

A = \begin{vmatrix} 1 & 2 & 3 & 4 & 5 \end{vmatrix}

c = 0, 0, 1, 1, 0, 1, 1, 1

[2\ 3\ 4\ 5\ 6]

n \equiv \text{any logical vector}

(n_i \equiv 0 \text{ or } 1)

P = \begin{bmatrix} 0 & 1 & 1 \\ 1 & 0 & 1 \end{bmatrix}

p = 1, 0, 1, 0, 1

q \equiv 1, 0, 1

r = +, -, \times, \div

```

#### Examples 3

```

a_1 = -6

b + q = 4, 2, 2

A_0 = 0, 1, 2

r_0 \equiv +

b r_0 q = 4, 2, 2

P^1 = q

a - A^0 \equiv 7, -7, 3, -7, -1

|a - A^0 \equiv 7, 7, 3, 7, 1

2 \times \boldsymbol{b} \equiv \boldsymbol{b} \times 2 \equiv 6, 4, 2

b \times b = 9, 4, 1

-3.6 = 3.6

| q - 3 \equiv 2, 3, 2

\begin{bmatrix} -3.6 = -4 \\ -3.6 = -3 \end{bmatrix}

\begin{bmatrix}

3.6 &\equiv 3 \\

3.6 &\equiv 4

\end{bmatrix}

\lfloor a \div 2 \equiv 3, -3, 2, -2, 1

a \div 2 = 4, -3, 3, -2, 2

7 \mid 21 \equiv 0

2 \mid a = 2 \mid a \times a = 1, 0, 1, 0, 1

7 \mid 19 \equiv 5

q \wedge P^0 \equiv 0, 0, 1

p_0 \wedge q_0 \equiv 1

q \wedge 2 \mid b \equiv q \equiv A_1^0 \wedge q

p_0 \vee q_0 \equiv 1

q \vee P^0 = 1, 1, 1

q \vee 2 \mid b = q

\sim q \wedge P^0 \equiv \bar{q} \vee \bar{P}^0 \equiv 1, 1, 0

\bar{q}_0 = \sim q_0 = 0

\hat{b} < A_1 \equiv 0, 0, 1

q_0 \neq p \equiv \bar{p} \equiv \sim q_0 = p

a_4 \leq b_0 = 1

2 < A_1 \equiv 0, 0, 1

```

$$P \stackrel{\triangle}{=} 2 4 6 8 10 \qquad P \stackrel{\triangle}{=} q = \sim P \stackrel{\vee}{\downarrow} q = 0, 1$$

$$P = (0, 1) \oplus (1, 0) \oplus (1, 1) = \epsilon^{1}(2) \oplus \epsilon^{0}(2) \oplus \epsilon^{0.1}(2)$$

$$A = \iota^{0}(3) \oplus \iota^{1}(3) \oplus \iota^{2}(3) \oplus \iota^{2}(3) \oplus \iota^{4}(3)$$

$$p, b = 1, 0, 1, 0, 1, 3, 2, 1 \qquad q/b = 3, 1$$

$$(2 \mid A^{0})/A^{1} = 2, 4 \qquad (a > 0)/a = 7, 5, 3$$

$$p/A = \begin{bmatrix} 0 & 2 & 4 \\ 1 & 3 & 5 \\ 2 & 4 & 6 \end{bmatrix} = A_{0,2,4}$$

$$q//A = \begin{bmatrix} 0 & 1 & 2 & 3 & 4 \\ 2 & 3 & 4 & 5 & 6 \end{bmatrix} = A^{0,2}$$

$$E/A = 0, 1, 2, 3, 4, 1, 2, 3, 4, 5, 2, 3, 4, 5, 6$$

$$E(4, 2) \setminus a, b = \begin{bmatrix} 7 - 6 \\ 5 - 4 \\ 3 & 3 \\ 2 & 1 \end{bmatrix}$$

$/a; p; A^{0}/\equiv 0, -6, 2, -4, 4$  $/b; p_0; q/ \equiv q$  $a_{12(2)} \equiv 5, -4$  $a_{0,3,1} \equiv 7, -4, -6$  $b_q = 2, 3, 2$  $\alpha/p = 1, 0, 0, 0, 0$  $\alpha/\bar{c} = 1, 1, 0, 0, 0, 0, 0, 0$  $+/\alpha/\bar{n} =$  number of leading zeros in  $n = \nu n$  or index of leading 1 in n

For brevity, branch and specification statements are sometimes combined in the form

$$z: y \leftarrow x$$

implying that y is specified by x and is then compared with z to determine a branch.

The operand types and elementary operators employed are defined in Table 1, together with examples. These examples permit Table 1 to be studied by itself before proceeding to the more complex expressions in the programs.

In a compound expression such as

$$(x \times y + z) - q \wedge \sim r$$

the order of execution of the elementary operations is determined by parentheses in the usual way and any remaining ambiguity is resolved by proceeding from right to left, *no priorities* being accorded to multiplication or any other operator. This convention applies, in particular, to Table 1 itself.

The convenience of the right-to-left order of execution is indicated by the paucity of parentheses in the programs. As an example, consider line 5 of the *CPU* program:

$$\omega^{24}/p \leftarrow (24) \top 2 + \perp \omega^{24}/p$$

.

Proceeding from right to left, the last 24 bits of the vector p are selected, the base-2 value of the resulting vector is taken and added to 2, and finally the 24-bit representation of the sum respecifies the last 24 bits of p.

In complex logical expressions, the right-to-left convention permits convenient interpretation from left to right; for example, the expression

$$p \lor q \lor r \land s \land t = 3$$

is interpreted as indicated by the tree shown in Figure 1.

No elision of operator symbols is permitted; consequently, the names of variables can, without ambiguity, consist of any number of alphabetic characters, including spaces. For brevity, single characters are used for all variables except for those which occur infrequently, such as the panel switches occurring in CP, the control panel program. All variable names are in italics: light-face lower case for scalars, boldface lower case for vectors, and boldface upper case for matrices. Literal alphabetic values (e.g., "stop" and "operate" on lines 12 and 13 of the CP program) are denoted by roman type.

In order to reduce the number of variable symbols assigned to local counters and other intermediate variables, certain symbols (including i, j, k, i, j, and k) will be used only as local variables, i.e., the value of any such variable will be relevant only in the program in which it occurs and will not affect or be affected by any variable of the same name occurring in another program. A family of matrices will be denoted by a pre-superscript as, for

Figure 1 Tree representation of a compound statement

example, 'J, in line 20 of MAC' (j; k), the memory access program.

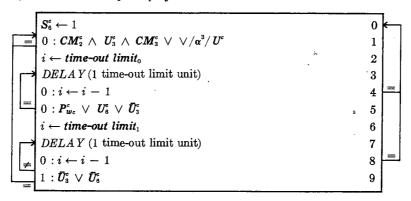

The system description comprises a set of tables and programs. Programs include system programs and defined operations. All system programs operate concurrently and continuously, with precisely one line active in each program at all times. This active line will often be a dwell of the form shown in Figure 2. The program breaks from the dwell only when the variable x is set to a nonzero value by some other program in the system.

A defined operation is a program which operates only when invoked by some other program. It can be distinguished from a system program by the presence of exit arrows. When called, a defined operation constitutes the active line of the program it is serving, and will itself have precisely one line active at a time until an exit is reached.

Variables occurring in the name of a defined operation (for example, j and k in the case of  $MAC^i(j;k)$ ) are dummy variables whose values are determined by the values of the variables occurring in any particular use of the defined operation. Thus, the performance of line d3 of EXC (that is,  $MAC^0$  ( $a_2$ , 2, f, d;  $\omega^{16}/R^{a_1}$ )) executes  $MAC^0$  with  $j=(a_2, 2, f, d)$  and with  $k=\omega^{16}/R^{a_1}$ . A study of MAC will show that this causes 2 bytes of data, fetched from the memory location starting at  $a_2$ , to be transferred to the last sixteen positions of the general register whose index is  $a_1$ .

All components of the formal system are listed in Table 2. The text and figures, and the tables not listed, are intended for exposition only.

Table 2 Components of formal description

| System p    | rograms                                   |                 |                 |                                  |            |

|-------------|-------------------------------------------|-----------------|-----------------|----------------------------------|------------|

|             |                                           | page            |                 |                                  | page       |

| BMT         | Burst-mode timer                          | 261             | HFC $c$         | Hardware failure in channels     | <b>261</b> |

| $CH^{c}$    | Channels                                  | <b>26</b> 1     | IOIE            | I/O interruption entry           | 261        |

| CP          | Control panel                             | 259             | IPL             | Initial program load             | 259        |

| CPU         | Central processing unit                   | 259             | MCIE            | Machine check interruption entry | 259        |

| EIE         | External interruption entry               | <b>259</b>      | T               | Timer                            | 259        |

| EP          | Emergency pull                            | 259             | $TOL^{c}$       | Time-out limiters                | 261        |

| ES          | External signals                          | 259             | TU              | Timer update                     | 259        |

| Defined o   | perations                                 | page            |                 |                                  | page       |

| DELA        | Y                                         | *               | MODEI           | L-DEPENDENT RESET                | *          |

| DIAGN       | IOSE                                      | *               | POWEI           | R-OFF SEQUENCE                   | *          |

| EXC         | Instruction execution                     | 240             | POWEI           | R-ON SEQUENCE                    | •          |

| MAC'        | j; k) Memory access                       | 259             | RESET           | •                                | <b>259</b> |

| MALF        | UNCTION RESET                             | *               | SYSTE           | M STOP                           | *          |

| * These ope | rations are not detailed in this descript | ion.            |                 |                                  |            |

| Tables      |                                           |                 |                 |                                  | page       |

| Table 3     | System reference table for pro            | grams and var   | riables: symbol | and dimension columns only       | 250        |

| Table 5     | Navigation matrix $N$ and refe            | rence table: fi | rst 11 columns  | (navigation matrix) only         | 256        |

| Table 6     | Operation decoding matrix O:              | numerical ent   | tries only      |                                  | 258        |

Figure 2 Dwell

x:0

# Table 4 Central processing unit

|                                      | CPU   |

|--------------------------------------|-------|

| Functions                            | lines |

| Initial-program-load<br>dwell        | 0     |

| Instruction fetch                    | 1-7   |

| Instruction interpre-                | 8-10  |

| tation                               |       |

| Effective address cal-<br>culation   | 11–19 |

| Instruction execution                | 20-21 |

| Entry of program interruption        | 22-24 |

| Interruption service                 | 25-33 |

| Single-step, stop, and<br>wait tests | 34–36 |

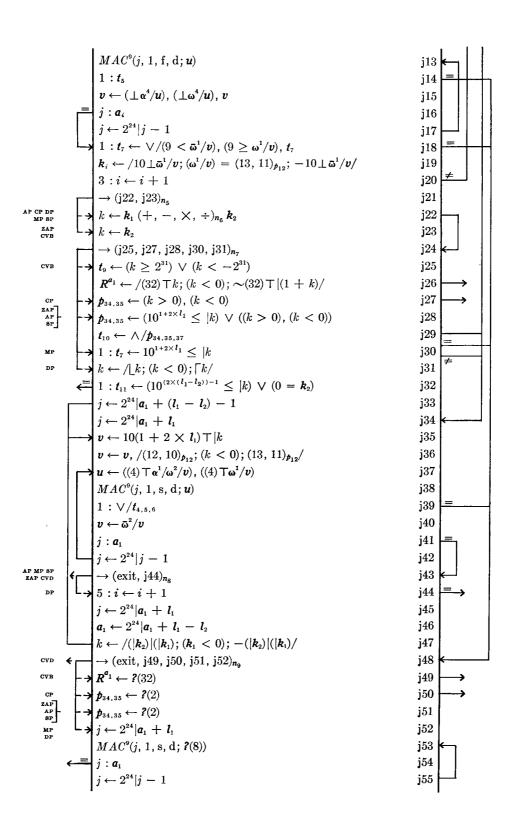

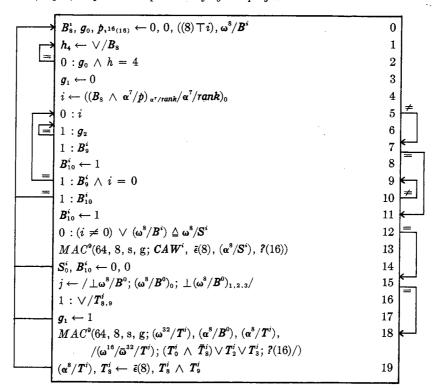

**CPU** program

instruction fetch (lines 1—7)

instruction interpretation (lines 8—10)

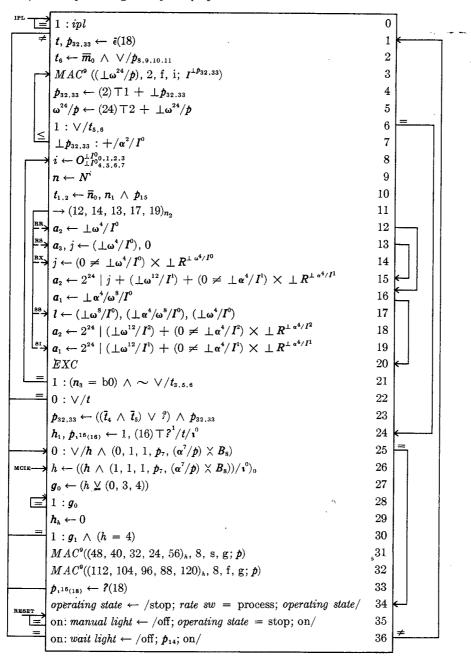

## The central processing unit

The central processing system comprises the nine system programs shown on page 259, and the defined operations listed in Table 2. An overall view of the system can be gained from Table 3, which lists all variables occurring in the programs, indicates the meaning or significance of each symbol and the dimensions of each vector or matrix variable, and provides reference to every program statement (or entire program) in which each variable is specified or used. Since the range of each variable is readily deduced from its use in the programs, ranges are not explicitly specified in the table. Most of the variables are logical (i.e., have the range 0, 1), but some, such as the components of a, m, and N, are not. The ranges of the components of some arrays (e.g., N) are not all alike.

Although Table 3 is designed for reference, it will also repay careful initial study. It shows, for example, that the memory M behaves as a 9-bit wide memory of at most  $2^{24}$  8-bit bytes with parity, that each block of  $2^{11}$  bytes of M may be protected by a 4-bit protection key  $K^i$ , and that 16 single-word general registers R and 4 double-word floating-point registers F are provided. All of the more detailed information on the treatment of the variables (such as the formats used in instruction addresses) is immediately available in the programs.

The core of the system is the CPU program, which describes the sequencing and execution of instructions and the servicing of interruptions. The functional segments of this program are listed in Table 4.

An instruction may be 1, 2, or 3 half-words long and is fetched by lines 3-7 (using the MAC operation detailed on page 259), two bytes at a time, from memory locations specified by the instruction counter represented by  $\omega^{24}/p$ , the last 24 bits of the program status word p. For each half-word fetched, the instruction length code  $(p_{32,33})$  is augmented by 1 (line 4) and the instruction address by 2. The sum of the first 2 bits of the first half-word plus 1 determines (on line 7) the number of half-words fetched.

Line 2 enters a specification exception if the protection feature is not installed ( $m_0 = 0$ ) and any of positions 8-11 of p are nonzero. Addressing and specification exceptions are detected by lines 7-8 of the MAC operation and are entered (MAC line 15) into  $t_5$  and  $t_6$ , respectively. Either of these errors subsequently causes a branch from CPU line 6 to line 24, skipping the instruction execution phase and any remaining portion of the fetch.

If the fetch concludes without error, lines 8-9 interpret the instruction by selecting from the navigation matrix N (Table 5) a row  $N^i$  to specify the vector n used in the subsequent control of the instruction execution phase. The row of N selected is determined by the particular element of the operation decoding matrix O (Table 6) selected by the 8-bit operation code in the first byte of the instruction. Table 6 displays the mnemonics

used for the instructions as well as the index to N, which is the only formal part of the matrix O. Similarly, Table 5 includes much informal information in addition to the formal specification of the matrix N.

Except for its first two components, the navigation vector n is of formal interest only, since the sequences it determines in the CPU program (line 11) and in the EXC operation are also indicated informally by broken-line arrows and labels. If the 8-bit operation code corresponds to no installed operation, then  $n_0 = 0$  and an operation exception exists (line 10); if the operation is privileged ( $n_1 = 1$ ) and if  $p_{15} = 1$  (that is, the processor is in the problem state as opposed to the supervisor state), a privileged operation exception exists.

The manner of specifying the operands of an instruction is a function of the format of that instruction. Most instructions specify two operands; the effective addresses of the first and second operands are computed as  $a_1$  and  $a_2$ , respectively. Normally, the addresses are used to select two general registers (RR format), a register and storage in memory (RS), a register and storage with a second register for indexing (RX), two areas in storage (SS) or storage and immediate data from the instruction itself (SI), all as indicated in Table 7. However, since many exceptions exist, Table 7 should be considered as a guide only, all operands being explicitly defined in EXC. Some instructions in the RS format use a third address  $a_3$ . A terminal R and a terminal I in instruction mnemonics usually indicate the RR and SI formats, respectively.

For instructions in the SS format, the lengths of the operands are defined by line 17;  $l_1 + 1$  and  $l_2 + 1$  are the lengths (in bytes) of the first and second operands, and  $l_0 + 1$  is the length for some instructions in which a single length is required. Again, the matrix N (and hence n) provides (via CPU line 11) the formal specification of the format used by each instruction.

The calculation of the effective addresses is straightforward and will be discussed only for the RX and RS cases. In the latter case, the second operand address  $a_2$  is determined by the second half-word of the instruction and is formed by adding to the value of its last 12 bits  $(\perp \omega^{12}/I^1)$  the value of the general register selected by its first 4 bits  $(\perp R^{\perp \alpha^*/I^*})$ , unless the zeroth register is selected  $(0 = \perp \alpha^4/I^1)$ , in which case zero is added. Finally, the residue of this sum modulo  $2^{24}$  specifies  $a_2$ . The first and third operand addresses are determined by the values of groups of 4 bits in the first half-word,  $\perp \alpha^4/\omega^4/I^0$  and  $\perp \omega^4/I^0$ , respectively. The RX format differs only in that the index quantity contained in the general register selected by the last 4 bits of the first half-word is (again, unless the zeroth register is selected) also added to the sum used to determine  $a_2$ , and in that the third address is not applicable.

The calculation of the effective address is immediately followed by a use of the defined operation EXC on line 20. This operation begins with a branch from line 0 to line  $n_3$ , that is, to the segment

effective address calculation (lines 11—19)

instruction execution (lines 20—21)

of the EXC operation appropriate to the particular instruction being executed. For example, if the instruction is LR, then  $n_3$  is specified by  $N_3^{71}$ , and  $n_3 = d0$ . This is also indicated informally by the "LR" written to the left of line d0.

To continue the example, line d0 specifies the value of general register  $R^{a_1}$  by the value of  $R^{a_2}$ , and the exit arrow on the same line indicates that EXC is complete.

The execute instruction (EX) beginning on line b0, furnishes a somewhat more complex example of the execution phase. Except that the length code  $p_{32,33}$  and the instruction counter  $\omega^{24}/p$  are not disturbed, lines b0-3 are like the instruction fetch (CPU 3-7) and therefore load the instruction register with the data beginning at byte address  $a_2$  in memory. Since  $n_3 = b0$  in this case, line 21 of CPU subsequently causes (unless a program interruption has been entered in t, either on line b5 or by use of MAC on line b1) a branch to line 8, thus interpreting and executing the instruction just fetched by the ex instruction, without disturbing the instruction counter. If this subject instruction is itself an Ex. it has the operation code 0100 0100, and line b5 therefore enters an execute exception and line 21 does not cause a branch, thus aborting the execution of the subject ex instruction. The phrase  $\bar{t}_5 \wedge \bar{t}_6$  in line b5 prevents a spurious execute exception if addressing or specification exceptions have already occurred.

If the first operand address of EX is nonzero, then line b4 will or the last byte of general register  $R^{a_1}$  with the last byte of the first half-word of the subject instruction. This permits a programmer to specify such parameters as length, index, or immediate data in the subject instruction indirectly via  $R^{a_1}$ .

If no program interruption has been generated by the preceding fetch and execution, each component of t will be zero, and lines 23 and 24 will be skipped. Otherwise line 24 presents the interruption by setting  $h_1$  to 1 and entering an appropriate code in positions 16-31 of p. Thus, if the interruption is occasioned by an addressing exception,  $t_5 = 1$ , the expression  $t/\tau^0$  yields 5, and its base 2 representation (namely, 0000 0000 0000 0101) is entered in p. If multiple causes of program interruption occur, then one of the appropriate codes will be selected at random and stored in p. For example, if  $t_5 = t_6 = 1$ , then  $t/\tau^0 = (5, 6)$  and  $t/\tau^0 = (5, 6)$  selects one of 5 and 6.

If the cause of the program interruption entry is neither  $t_4$  nor  $t_5$  (that is, neither a protection nor an addressing exception), then the instruction length code  $p_{32,33}$  is unchanged by line 23; otherwise line 23 may set the length code to zero.

Other types of interruptions are entered in other components of h by other programs (listed in the reference column of Table 3) whose details will be considered later.

An interruption service places an appropriate code in bits 16-31 of p, stores p in memory at one of five fixed locations determined by the type of interruption (line 31), and finally respecifies p (line 32) from one of five other fixed memory locations. Since

entry of program interruption (lines 22—24)

interruption service (lines 25—33)

this respecifies the instruction counter  $\omega^{24}/p$ , it occasions an alteration in the normal sequence of instructions.

Interruption servicing is skipped if the expression

$$\vee/h \wedge (0, 1, 1, p_7, (\alpha^7/p) \times B_8)$$

(line 25) has the value zero. The vector  $(0, 1, 1, p_7, (\alpha^7/p) \times B_8)$  is therefore a mask which causes certain components of h to be ignored. Thus  $h_0$  (machine check interruption) is always ignored at this point,  $h_1$  and  $h_2$  (program and supervisor call interruptions) never are,  $h_3$  (external) is ignored if  $p_7 = 0$ , and  $h_4$  (I/O) is ignored unless an interruption is being presented (in  $B_8$ ) by one of the channels for which the corresponding mask bit in  $\alpha^7/p$  is set to 1.

If there is an acceptable interruption, then line 26 determines h as the index (in h) of the interruption to be serviced. The queue discipline in h is not first-in first-out but rather strict priority (according to position in h) of the unmasked components of h presented.

If h = 0, 3, or 4 (machine check, external, or I/O), then  $g_0$  is set to signal the appropriate program (MCIE, EIE, or IOIE) to enter the appropriate data in bits 16–31 of p, while the CPU program dwells on line 28. Then the accepted interruption indication is reset on line 29. In certain situations, an I/O channel is unable to present an indicated interruption at the time it is accepted by the CPU; this is signalled by the IOIE program by setting  $g_1$  to 1 before resetting  $g_0$  to 0, thus aborting the interruption by the branch on line 30. In any event, line 25 is executed again so that all outstanding unmasked interruptions are serviced in turn before continuing to line 34.

Whenever the program status word p is loaded from memory, bits 16-33 (the interruption code and instruction length code) are indeterminate as shown by CPU 33, IPL 8, and EXC a26.

If the operating state is set to "stop", then the CPU dwells on line 35 with the manual light "on". Events which set the operating state are listed in Table 3. These include line 34 of the CPU which sets it to "stop" if the rate switch is not set to "process", e.g., if set to "single-step".

Subsequent to the dwell on line 35, the behavior is determined by the wait bit  $p_{14}$ ; if  $p_{14} = 0$ , the wait light is turned "off" and the next instruction fetch is begun (branch from line 36 to line 1); if  $p_{14} = 1$ , the wait light is turned "on" and the interruption service phase is entered at line 25. Hence if  $p_{14} = 1$ , the CPU "waits", executing no further instructions until an external or I/O interruption or initial program load replaces p with a value such that  $p_{14} = 0$ .

The computer memory is initially loaded by the IPL program which resets (line 1) the CPU to the dwell at line 0, where it remains until the loading (effected by an I/O channel) is complete, as signalled by the setting of the variable ipl to zero. The branch to line 25 shows that when loading is complete, operation is resumed with interruption service rather than with the instruction fetch.

single-step, stop and wait tests (lines 34—36)

initial-programload dwell (line 0) memory access operation

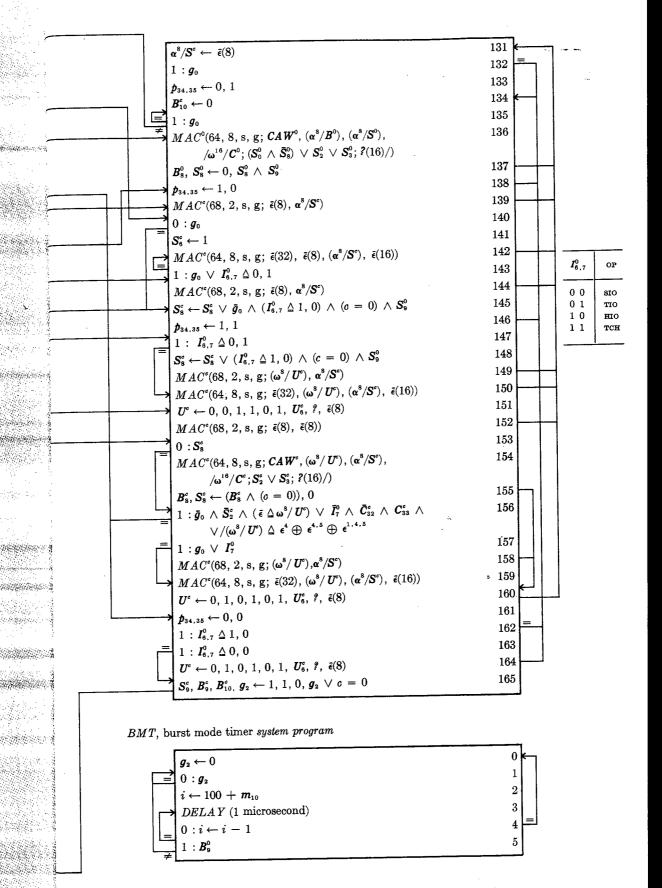

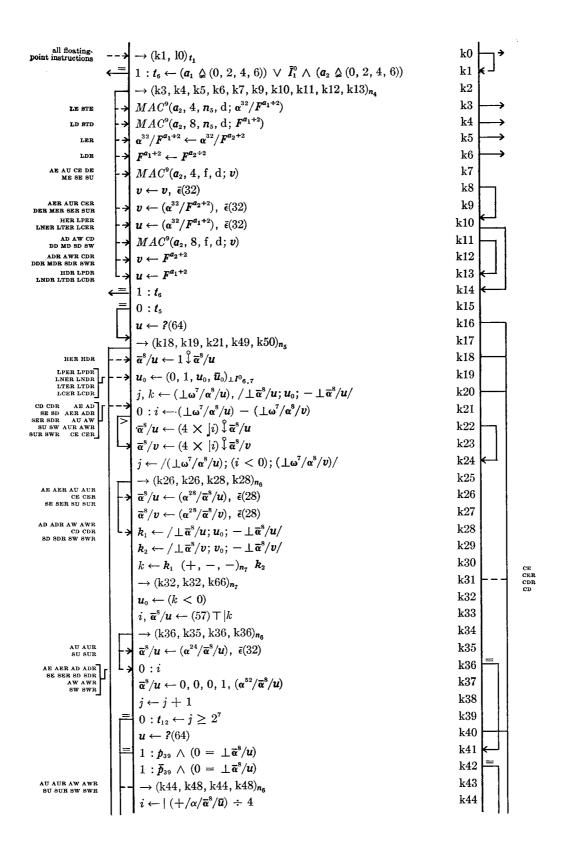

The MAC operation, which occurs in the instruction fetch and throughout the EXC operation, serves to fetch from or store in memory a specified number of bytes beginning at a specified address. Because it incorporates certain tests and other functions, it warrants a detailed scrutiny.

The general form of the MAC operation is  $MAC^{i}$  (j; k), where i specifies one of nine identical but independent MAC programs, i = 9 for the CPU memory-access, i = 8 for the interval timer, and i = 0-6 for the channels; where k is the vector involved in the transfer to or from memory; and where j is a four-component vector specifying the address in memory  $(j_0)$ , the number of bytes transferred  $(j_1)$ , the performance of a fetch  $(j_2 = f)$  or store  $(j_2 = s)$ , and the type of address being treated  $(j_3 = d)$  for data address, i for instruction address, i for a machinegenerated [i.e., fixed] address, and i for hold, which prevents any of the other  $MAC^{i}$  programs from operating until the current  $MAC^{i}$  program has been used again with  $j_3 \neq h$ ).

memory access priority

Since the several  $MAC^i$  programs all use the same memory, they must observe a queue discipline. It is controlled by the queue vector  $\mathbf{q}$  and the request vector  $\mathbf{r}$ . When  $MAC^i$  is invoked by any system program (e.g.,  $MAC^0$  in CPU line 3), then a request for service is entered (line 0) by setting  $\mathbf{r}_i$  to 1. If the queue is empty, the request is also entered in  $\mathbf{q}_i$ . In any case, the  $MAC^i$  program dwells on line 1 until i is recognized as the "first" nonzero entry in the queue. The queue discipline is not first-in first-out, but is in order by position in a permutation of  $\mathbf{q}$  specified by the vector  $\mathbf{rank}$ , which gives priority according to the index i, except that i = 0 (the multiplexor channel) may be assigned out of order. This implies that the channels have priority over the interval timer which has priority over the CPU.

Any request for service which is not entered directly in q on line 0 is entered from r by line 24. If  $j_3 \neq h$ , then q is respecified by r (with  $r_i$  already set to zero by line 2) except that a CPU request is entered in  $q_0$  only if w=0. The variable w is controlled (line 2) only by  $MAC^8$ , the timer update memory-access, and it remains at 0 or 1 according to whether the last use of  $MAC^8$  was for a store or for a fetch. This excludes the CPU from memory during the updating of the interval counter (TU lines 1, 3) and prevents the inadvertent overwriting (by TU line 3) of a new setting of the interval timer counter by a CPU "store" instruction. However, the use of memory by I/O is not excluded by w.

If  $j_3 = h$ , line 24 leaves q unchanged and therefore prevents any other MAC from being executed until after the next use of the same MAC with  $j_3 \neq h$ . The use of  $j_3 = h$  occurs only in the instruction TS (test and set) as follows (EXC lines a29, 30)

$$MAC^{9}(a_{1}, 1, f, h; u)$$

$MAC^{9}(a_{1}, 1, s, d; \epsilon(8)).$

Thus, the addressed byte is set immediately following a test of its value, before any other access to memory can occur.

The first  $2^{12}$  bytes of memory are normally used for special purposes by the machine (e.g., 48, 40, 32, 24, and 56 are used to store p on line 31 of the CPU program) and by the supervisory program. Any address  $j_0$  in this region is automatically prefixed (MAC lines 3,4) by a 12-bit prefix selected from either the main or alternate prefix (having wired-in values) according to the setting of the prefix trigger, which is set during the initial program loading (IPL line 3). It must be emphasized that every memory address (including those used in I/O) below  $2^{12}$  is modified in this way, although this fact will not be referred to again in the text.

The effect of line 6 is to set the operating state to "stop" if all but the last bits of the address switch on the console agree with the specified address  $j_0$ , but line 6 is skipped if the address compare switch is on "normal" or if it is set to "instruction" and  $j_3$  does not specify that  $j_0$  is an instruction address.

Lines 7-11 specify three types of exception conditions. A specification exception is indicated (line 7) if the address  $j_0$  is not divisible by the number of bytes  $j_1$ . An addressing exception is indicated (line 8) if the address  $j_0$  exceeds the size of memory, and in this event the address  $j_0$  is respecified for all subsequent purposes by an arbitrary value within the range of the memory (line 9). A protection exception is indicated (lines 10,11) if the machine has the protection feature ( $m_0 = 1$ ) and the memory-access is of the store data type ( $j_{2,3} = s$ , d) and the keys  $u_0$  and  $u_1$  differ and neither is zero, where  $u_0$  is the protection key in the memory bank addressed by  $j_0$ , and  $u_1$  is either the protection key in p (in the case of a CPU memory-access) or the protection key in the appropriate channel address word (in an I/O memory-access).

If there are multiple exceptions, line 13 chooses some one of them to enter into s and thence into the program exceptions vector t (in the case of CPU or timer memory-access) or in the channel status word S' (in the case of a channel). If the error is a specification exception ( $s_0 = 1$ ) or if the operation is a store, then line 17 skips all further steps except to respecify the queue (line 24). Otherwise, i.e., on a fetch operation with an addressing exception, in which the address  $j_0$  has been respecified arbitrarily (line 9), the (meaningless) fetch from memory proceeds.

If no exception occurs, or if a machine-generated address is being treated, line 12 skips the entry of exceptions, branching directly to line 18 which chooses line 23 for store and 19 for fetch. Line 23 stores the specified vector k together with the appropriate parity bits in the specified rows of M. Line 19 fetches the appropriate rows of M to specify the matrix  $^{i}J$ . The row list of the last 8 columns of  $^{i}J$  specifies k, and the parity bits are available (e.g. to the channel) in  $^{i}J_{0}$ . In the case of a CPU or a TU memory-access, line 22 checks the parity of the data fetched from memory and signals an error by setting component 9 or 8 of the machine failure vector f.

address modification and comparison

exceptions

other central processing system programs

control panel and emergency pull programs

external interruption entry program

machine check interruption entry program

The details of the control panel, the interruption entries, the interval timer, the initial program load, and the EXC operation will now be treated in that order. At this point, however, the reader should be equally prepared to approach them in any other desired order. It must be re-emphasized that all system programs, including the CPU program, run concurrently.

The normal dwell of the CP program (lines 4,5) is broken by depression of the power-off key (line 4) or by depression of a console button  $b_i$  or by a pulse on one of the IPL in-lines  $e_4$  or  $e_5$ . Line 6 determines b as the index (with respect to  $e_4$ ,  $e_5$ , b) of the signal to be serviced, line 7 dwells until the signal returns to zero, and line 8 branches to the appropriate program segment.

The last four buttons are ineffective if the machine is in the "operate" state (line 13), but otherwise perform the straightforward functions detailed in lines 15–25. The stop key (line 12) causes the CPU to dwell the next time it reaches line 35; the interrupt key sets the console interrupt which (as indicated in Table 3) is used in the EIE program to enter an external interruption; the IPL in-lines, the load key and the reset key all reset the system (line 9), and all but the latter set ipl, releasing the IPL program from its normal dwell.

The *EP* program serves to stop the entire system until the *emergency pull switch* is restored, whereupon it sets the *CP* program to line 1, to dwell until the *power-on key* is depressed.

The timing signal in-lines  $\omega^6/E^3$  are momentary pulses ( $\frac{1}{2}$  to 1 microsecond) supplied from some data transmission line, perhaps the output signals  $E^2$  of some co-operating computer. The ES program shows the latches external signals being set by  $\omega^6/E^3$ . Similarly, EIE shows the timer alarm, console interrupt, and external signals being entered as interruptions. If any of these signals appear, EIE line 0 sets  $h_3$ . The CPU program will eventually recognize  $h_3$  and set h=3 and  $g_0=1$  (lines 26,27), thus breaking the dwell on lines 0 and 1 of the EIE program. Line 2 then enters the eight external interruptions in p and line 3 resets those signals entered, but does not reset any which may have come on during the brief interval since the entry operation on the preceding line. The reset of  $g_0$  on line 4 frees the CPU from its dwell on line 28.

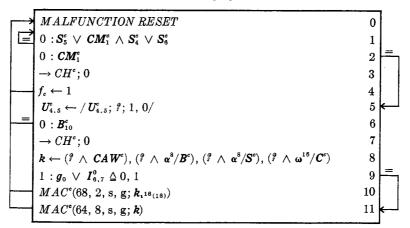

The entry of a machine check (i.e., a hardware failure) is radically different, since, after setting  $h_0$ , it preempts the CPU by causing a branch to CPU line 26. The MCIE program also sends a momentary signal on the machine-check out-line  $e_3$  (which may be connected as an input to some co-operating computer), enters zeros as the interruption code in p, performs a diagnosis, stores certain machine registers (referred to as cpu status) in memory beginning at byte 128, and finally resets  $g_0$  (to free the CPU), the failure vector f, and any outstanding program and supervisor call interruptions (but not external or I/O interruptions). The machine failure is serviced (line 0) only when the machine check mask  $p_{13} = 1$ .

Indications of machine failure are entered in f from various sources, but only two are shown in this description. One occurs on line 4 of HFC for hardware failures in certain I/O channels. The second occurs on line 22 of MAC, and detects parity errors in data fetched from memory for the CPU or the interval timer. Parity checks are also made on R, F, and p, and at other points, but none of these are shown explicitly in the programs. Their inclusion would merely encumber the description.

The TU program is activated by the signal tick from the T program, but only if the CPU is not stopped at the dwell on lines 36-37, the rate switch is set to "process", and an RDD (read direct) instruction is not awaiting a hold-in signal on  $e_2$ . When activated, line 1 fetches the four bytes representing the interval timer counter, line 2 decreases it (modulo  $2^{32}$ ) by an amount dependent on the timer frequency which drives the T program, line 3 restores the new count to memory, and line 4 sets the timer alarm if the count has passed through zero. The execution of  $MAC^8$  on lines 1 and 3 will, of course, be deferred until all I/O requests for memory access have been serviced. Moreover, no CPU memory-access can intervene between TU lines 1 and 3 (see MAC lines 2, 24).

The IPL program dwells at line 0 until ipl (set only by CP line 10) becomes 1, whereupon the CPU is forced to its dwell at line 0, and the  $load\ light$  is turned "on". The further behavior depends upon which agency (IPL in-lines or load key) initiated the action. If it were the load key, the program would dwell (line 5) awaiting a satisfactory error-free channel-end signal from the I/O unit designated by the setting of the  $load\ unit\ switch$ , store  $load\ unit\ switch$  in memory at address 2, and load p from memory at address 0. If the initiating agency were one of the IPL in-lines, only the loading of p would be performed.

If a machine failure occurs in the loading, the *IPL* program dwells on line 9, regardless of the value of the machine check mask; otherwise, line 10 turns the load light to "off", the operating state to "operate", and ipl to zero. The role of I/O in the initial program load will be clarified in the third section; here it will suffice to remark that the I/O channels are reset by the *RESET* occurring on line 9 of the *CP* program, and the I/O unit designated by the load unit switch then begins to perform a read.

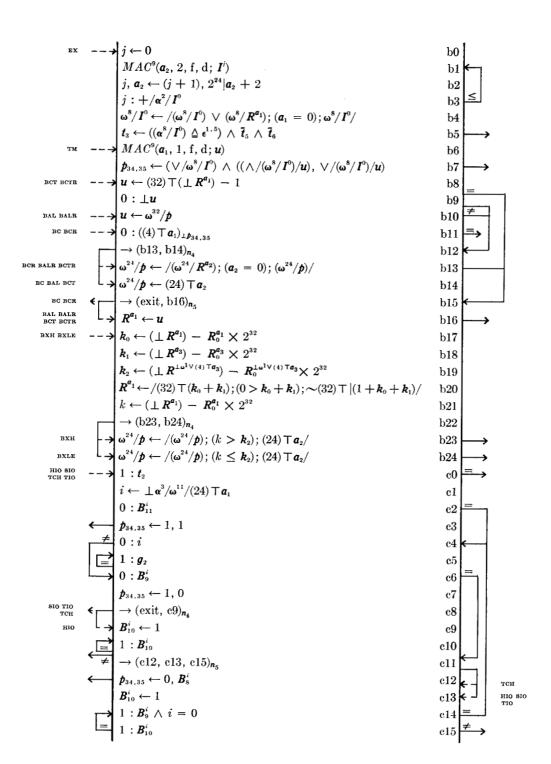

The 143 machine instructions described by the defined operation *EXC* are grouped in twelve families. Because there is little interaction with other programs, the interpretation is straightforward, and textual comment will therefore be limited to the more difficult cases.

Table 5 can facilitate reference in many ways. The final columns indicate the effect of each type of interruption on each instruction; it may *suppress* the instruction so that none of the result variables are affected, *terminate* it after some but not necessarily all of the results are respecified (and all results must be

timer and timer update programs

initial-program-load program

instruction execution operation considered unreliable), or allow it to *complete*. Since a protection exception  $t_4$  is occasioned only by storing in memory, the corresponding column of Table 5 can be used to identify all "store" type instructions; similarly, column  $t_5$  identifies all instructions which refer to memory. Other columns of Table 5 identify those instructions which set the condition code, general registers, and floating point registers.

status switching, read/write direct, diagnose (lines a0—34) ssm (set system mask) is a privileged operation executable only in the supervisor mode ( $p_{15} = 0$ ) as shown by the exit on line a1 and the setting of  $t_2$  on CPU line 10. Isk (insert storage key) and ssk (set storage key) are also privileged and are also suppressed (line a4) if the protection feature is not installed (that is,  $m_0 = 0$  and hence  $t_1 = \overline{n}_0 = \overline{m}_0 = 1$ ), if the address  $\pm \omega^{24}/R^{a_2}$  is outside the range of the memory, or if any of the last 4 bits of  $R^{a_2}$  are nonzero.

These last 4 bits of  $R^{a_2}$  are not otherwise relevant to ISK and SSK (see lines a6, 7) and the specification error test is intended to prevent the programmer from using them for other purposes, and hence to reserve them for use in possible modifications of SYSTEM/360, such as an extension of the length of the protection keys. The devious programmer can, of course, use a nonzero final half-byte in  $R^{a_2}$  to force a specification exception, but the prudent programmer will not. Similar tests will be found elsewhere (e.g., on the format of channel commands) and serve a similar function.

Since ssm, ssk, and isk are privileged instructions, only the supervisor program can set the system mask or set or refer to the memory protection keys  $K^i$ . spm (set program mask) is not privileged.

WRD (write direct) transfers one byte from memory to the direct control out-lines  $E^0$  and the immediate data byte from the instruction register to the timing signal out-lines  $E^2$ , and sets the write-out signal  $e_0$  to 1. The signals  $E^2$  and  $e_0$  are momentary;  $E^0$  remains unchanged until another WRD is executed. The test for suppression of the instruction (line a9) includes the term  $t_1$  because the direct control feature is optional and may not be installed, and the term  $t_2$  because WRD is privileged. Except for the dwell on line a17, the behavior of RDD (read direct) is similar. Normally, the outputs  $E^0$  and  $E^2$  of one computer are connected into the inputs  $E^1$  and  $E^3$  of a co-operating computer. Programs ES and EIE enter any nonzero signal on  $E^3$  as an interruption.

The diagnose instruction is privileged (as indicated by the presence of  $t_2$  on line a20) and may also be suppressed by an unsatisfactory address  $a_1$ . It performs a certain diagnosis of the hardware and then, for certain models, loads p using 8 bytes beginning at 112. LPSW (load program status word), which is also privileged, performs a similar load from memory at address  $a_1$ .

svc (supervisor call) forces an interruption by setting  $h_2$ ; the interruption code is the immediate data byte  $\omega^8/I^0$ , prefixed by 8 zeros.

Ts (test and set) simply fetches one byte u from memory (a29), sets the condition code to  $(0, u_0)$ , and sets the same byte in memory to all 1's. The significant characteristic of this instruction is that (because of the "hold" h in the first use of MAC) it sets the tested byte in memory before any other reference to memory can occur.

EX (execute) was discussed in conjunction with the CPU program. TM (test under mask) sets the condition code as shown on line b7. Thus, the code is (0, 0) if the immediate data byte  $(\omega^8/I^0)$  is entirely zero; otherwise, the first bit is set to 1 if all bits of  $(\omega^8/I^0)/u$  are 1, whereas the second bit is set if any bit of  $(\omega^8/I^0)/u$  is 1. The expression  $(\omega^8/I^0)/u$  denotes the components of the byte u from memory which are extracted by the nonzero bits of the immediate data byte.

The branch instructions set the instruction counter  $\omega^{24}/p$  conditionally as shown, and can therefore be used to alter the normal sequence of instruction execution. A full appreciation of BXH (branch on index high) and BXLE depends upon a knowledge of the 2's complement representation of signed numbers, which is also used in the fixed-point arithmetic instructions.

A logical vector (register)  $\boldsymbol{u}$  of dimension d represents any integer n in the range  $-2^{d-1}$  to  $2^{d-1}-1$  in the form

$$n = (\perp \mathbf{u}) - \mathbf{u}_0 \times 2^d.$$

For example, if d=3 the representation scheme is given in Table 8.

It is easily verified that the representation of a number n in the appropriate range is given by the statement

$$\boldsymbol{u} \leftarrow /(d) \top n; (n < 0); \sim (d) \top |n + 1/.$$

Arithmetic operations (such as the summation occurring in BXH (line b20)) may, however, produce a result outside the representable range. The representation shown above is, however, used even in this case. The matter is illustrated in Table 9 by examples computed for a dimension d=4.

For the BXH instruction, lines b17-19 show the specification of  $k_0$ ,  $k_1$ , and  $k_2$  as the signed numbers represented in general registers  $a_1$ ,  $a_3$ , and either  $a_3 + 1$  (if  $a_3$  is even) or  $a_3$  (if  $a_3$  is odd). Register  $a_1$  is then respecified by the 2's complement representation of the sum  $k_0 + k_1$ . The value of this result is compared with  $k_2$  (line b23) to determine whether to branch to  $a_2$ .

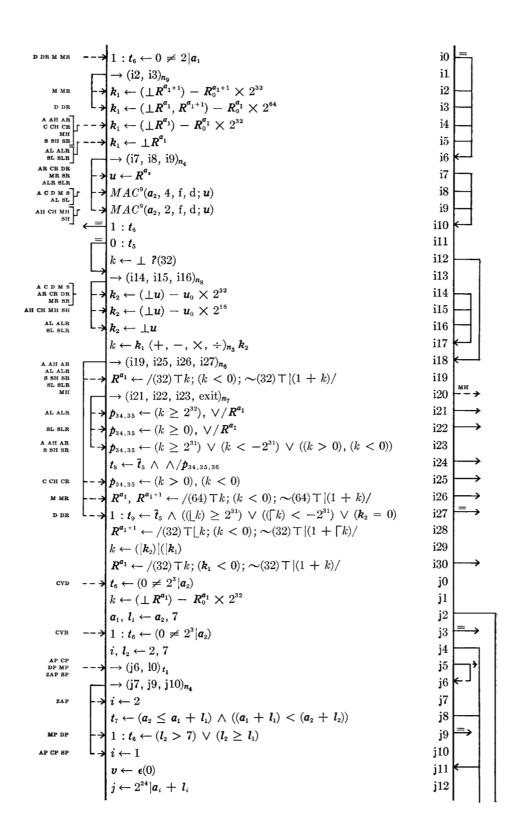

The four I/O instructions are all privileged (line c0), determine a channel address from the first three of the last eleven bits of the first operand address, test whether the indicated channel is operational (line c2), and conclude by setting the condition code to (1, 1) if it is not. If the channel selected is the multiplexor channel (i = 0) and a "burst mode" timer has not run out, then c5 dwells for a maximum of about 100 microseconds before testing (line c6) whether the channel is busy.

If the channel is busy, the condition code is set to (1, 0) on

branches, execute, test under mask (lines b0—24)

Table 8

| <i>n</i> | u     |

|----------|-------|

| 3        | 0 1 1 |

| $^2$     | 0 1 0 |

| 1        | 0 0 1 |

| 0        | 0 0 0 |

| -1       | 1 1 1 |

| -2       | 1 1 0 |

| -3       | 1 0 1 |

| -4       | 100   |

Table 9

| - Tuble 7                                                                                                  |                                                                |                                                                                               |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| n                                                                                                          | Repre-<br>senta-<br>tion                                       | Inter-<br>preta-<br>tion                                                                      |

| $ \begin{array}{r} 2^{3} + 1 \\ 2^{3} \\ 2^{3} - 1 \\ -2^{3} \\ -(2^{3} + 1) \\ -(2^{3} + 2) \end{array} $ | 1 0 0 1<br>1 0 0 0<br>0 1 1 1<br>1 0 0 0<br>0 1 1 1<br>0 1 1 0 | $   \begin{array}{r}     -6 \\     -7 \\     +7 \\     -8 \\     +7 \\     +6   \end{array} $ |

|                                                                                                            |                                                                |                                                                                               |

input/output (lines c0—15)

line c7, and all instructions but Hio (halt I/O) conclude; Hio proceeds to signal the channel to stop by setting  $B_{10}^i$  and then dwells until the channel resets it to zero.

If the channel is not busy, line c11 branches to conclude on line c12 for TCH (test channel), and otherwise to set  $B_{10}^i$  and dwell (c14, 15) awaiting a response from the channel. The dwell endures until either  $B_{10}^i$  is reset by the channel or until (in the case of the multiplexor channel only) the channel becomes busy ( $B_0^i = 1$ ). The latter case is followed by a repetition of the sequence from line c4. This repetition could recur many times due to short bursts of activity in the multiplexor channel instigated by I/O units already in operation. Further discussion of the I/O instructions will be deferred to the third section.

load and store general registers (lines d0—24) LH (load halfword) loads the last two bytes of  $R^{a_1}$  from memory and then, unless a specification exception has occurred in the fetch from memory, extends the sign bit  $R^{a_1}_{16}$  to the left to give the correct 2's complement representation in the entire register.

LPR (load positive), LNR (load negative), LTR (load and test) and LCR (load complement) illustrate the use of the 2's complement representation. Since line d11 sets the condition code to (1, 1) only in the event of overflow, line d12 indicates a fixed point overflow only if the overflow mask  $p_{36} = 1$ .

STM (store multiple) stores a number of general registers beginning with  $a_1$  and continuing in cyclic order through register  $a_3$ . A specification exception suppresses the instruction since it occurs on the first execution of line d14 before any data has been transferred, but in the event of either a protection or addressing exception all of the result field becomes unreliable (d19-24). LM (load multiple) behaves similarly except that a protection exception cannot occur.

shifts (lines e0—15) All single-length shifts operate on  $R^{a_1}$ ; all double-length shifts operate on the combined quantity  $R^{a_1}$ ,  $R^{a_1+1}$  and cause a specification error (which suppresses the instruction) if  $a_1$  is odd. The amount of shift is the residue modulo 64 of  $a_2$ ; zeros are introduced in the evacuated positions for all except the arithmetic right shifts.

All of the arithmetic shifts shift the entire quantity except the first bit (e8, 10) and set the condition code to (0, 1), (0, 0), or (1, 0) according as the result is <, =, or > zero, except that the left shifts set it to (1, 1) if a significant digit (i.e., in the 2's complement representation, one which differs from the leading bit) is lost in the shift (e7). In this event the left shifts also set a fixed point overflow exception (e9) if mask  $p_{36} = 1$ . The right shifts extend the sign bit (e11) to fill evacuated positions to give the correct representation of the result in 2's complement form.

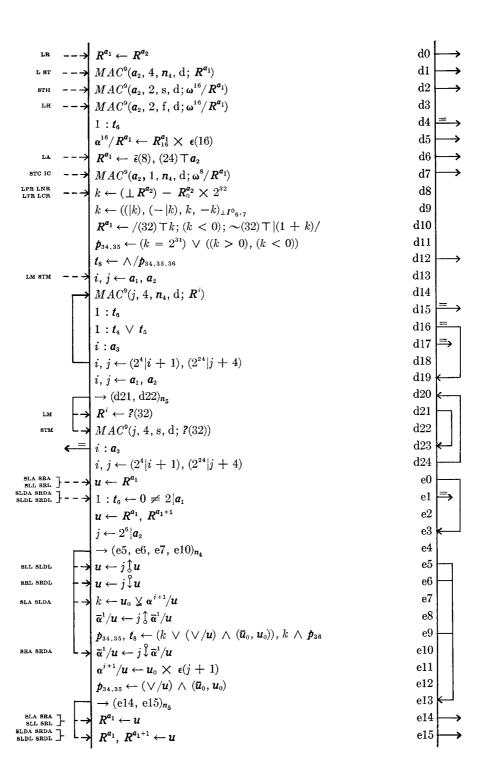

This family comprises four operations (compare logical, or, and, and exclusive-or) in four formats (RX, RR, SI, and SS). The first three formats are treated in lines f0-13. cl, clr, and cli merely set the condition code (f7); the rest perform the appropriate logical operation (f8) and set the condition code as shown on line f13, except that in the SI format the setting of the condition code

logical operations, compare logical (lines f0—32) is suppressed (f12) by a protection or addressing exception.

The SS format for logical operations (f14-32) operates byteby-byte from left to right. As in the LM and STM instructions, a protection or addressing exception will make the entire result field and the condition code unreliable (f27-32).

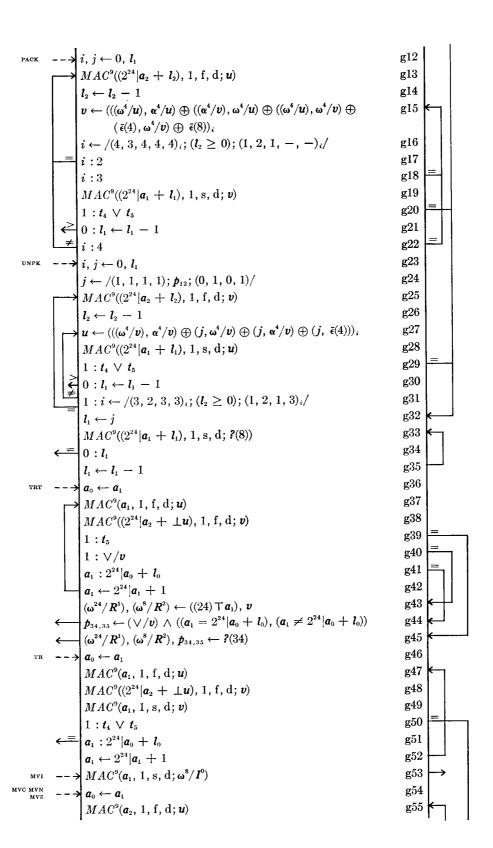

The instructions in this group treat the operands byte-by-byte, the first three (MVO, PACK, UNPK) in right-to-left order and the rest left-to-right. The single-byte uses of MAC involved cannot produce a specification exception; protection or addressing exceptions make unreliable the entire result field in memory, as well as the condition code when it is a result.

MVO (move with offset) moves the second field to the first field, off-setting it one-half byte to the left to leave the rightmost half-byte of the result field unchanged. Zero fill occurs (g9, 10) when the source field is exhausted, and conclusion occurs (g6) when the result field is exhausted.

PACK converts a decimal number in zoned format (one digit per byte with  $\alpha^4/byte$  as the zone bits, except for the low-order byte in which  $\alpha^4/byte$  represents the sign) into packed format (two digits per byte, namely,  $\alpha^4/byte$  and  $\omega^4/byte$ , except for the low-order byte in which  $\omega^4/byte$  represents the sign). Five operations, selected by the variable i (line g15), are used in constructing the packed bytes as follows:

- 0 the sign and digit of the low-order byte are interchanged;

- 1 the digit is placed in the right half of the byte;

- 2 the digit is placed in the left half of the byte;

- 3 a zero digit is placed in the left half of the byte;

- 4 zero digits are placed in both halves of the byte.

The variable i respecifies itself (line g16) by the ith component of (4, 3, 4, 4, 4) if the source field is exhausted, or by (1, 2, 1, -, -), if it is not. The process ends (g21) when the result field is completed.

UNPK (unpack) performs the operation converse to PACK. The program is analogous but simpler, since i has only four states.

The remaining instructions in this group scan the fields from left to right. TRT (translate and test) uses successive bytes from the first field as relative addresses in the second field until the byte fetched therefrom is nonzero; this byte and the current address to the first field are then stored in  $R^2$  and  $R^1$ , respectively (g43), and the condition code is set. TR (translate) replaces each byte of the first field by its correspondent selected from the second field. Mvz (for which  $I_6^0 = 1$ ) moves only the zone portion (i.e., the left half) of each byte; MvN moves the numeric portion.

ED uses the first field both as result and as a pattern to select successive bytes from the second source field and from a fill byte specified (h13) by the first byte of the pattern field. Each pattern byte is classified (h12) as "digit select", "significance start", "field separator", or "other" (class = 0, 1, 2, or 3); class then controls the subsequent assembly of the result byte.

move, pack, translate (lines g0—62)

edit (lines h0-37)

Except for a byte with a sign (i.e., a non-numeric right half), bytes from the source field are used one half-byte at a time, each half being prefixed by a standard zone j selected by  $p_{12}$  (lines h2, 17–22). The source byte thus constructed is used (h24–26) only if the numeric part is nonzero or if the current portion of the field is already significant (s = 1); otherwise the fill byte is used. The byte is constructed, and the source field is advanced, only when the class of the pattern byte is either a "digit select" or a "significance start" (h14). If the class is "other" and s = 1, the pattern byte is left unchanged (h15); otherwise the fill byte is inserted (h16).

The significance trigger s is set only on line h8. It is set to zero if j=0, that is, at the outset (h1) and also if the last byte used was from the source field and the numeric part was a plus sign (h9, 23). If j=1, then s is set according to the class of the preceding pattern byte, s changing from 1 to 0 only in the case of a "field separator" (class = 2), and from 0 to 1 only in the case of "significance start" (class = 1) or in the case of "digit select" if the last byte was chosen from the source field and was nonzero, as seen from the setting of  $\boldsymbol{u}$  on lines h10 and h21.

The final setting of the condition code is determined (h3) by s and i. The latter is set by a nonzero digit (h27) and reset (h7) by a "field separator." A data exception ( $t_7$ ) occurs if the left half of a source byte is non-numeric (h20), and terminates (h4) in the manner of protection and addressing exceptions. Since ED is an optional (decimal) feature, it is aborted (h0) if  $t_1 = 1$ , and is treated as an "undefined operation" by branching to line 10. EDMK (edit and mark) differs only in that the byte address of the first nonzero digit in the last nonzero field is entered (h30) in  $\mathbb{R}^1$ .

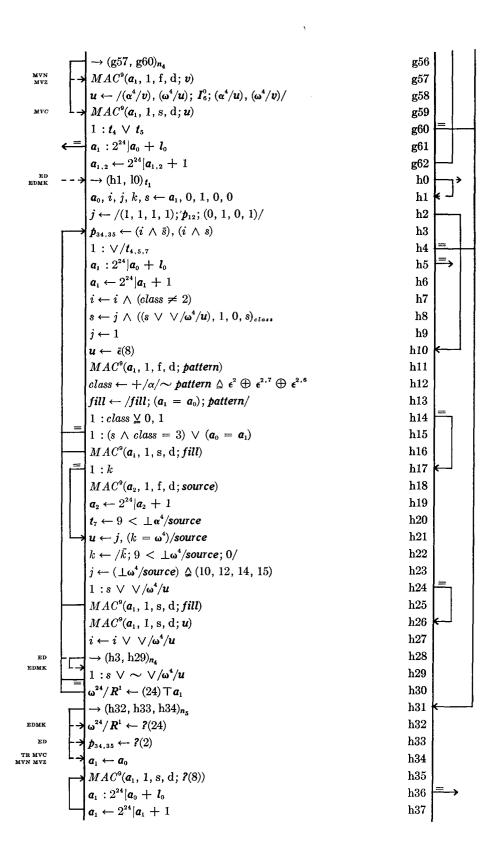

In this group of instructions, the first operand is taken from one or two general registers, determined by  $a_1$ . The second operand is chosen as  $R^{a_2}$  for the RR format instructions, as 2 bytes from memory at  $a_2$  for the half-word instructions, or as 4 bytes from memory for all others.

The arguments  $k_1$  and  $k_2$  are derived from the operands in two ways: as the base-2 value (i5, 16) in the "logical" group AL, ALR, SL, SLR, and as the 2's complement value (i4, 10) for all others.

A specification exception suppresses the instruction (i10). An addressing exception makes the result k questionable (i11, 12); otherwise k is the true result of the appropriate arithmetic operation on  $k_1$  and  $k_2$  (line i17).

The specification of the final result is illustrated by line i19. The treatment of results outside the representable range has already been discussed in the section devoted to branch instructions. The setting of the condition code and the exception conditions  $t_8$  and  $t_9$  is straightforward.

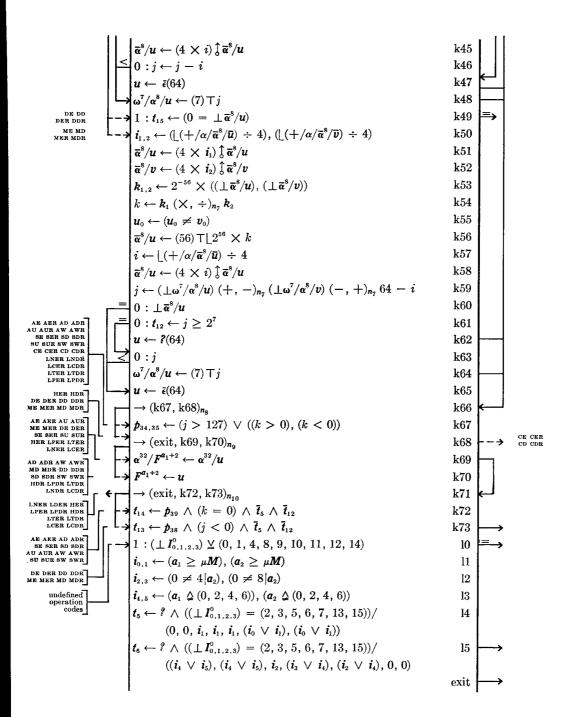

The intermediate result k is obtained (j22) by applying the appropriate arithmetic operation to the arguments  $k_1$  and  $k_2$  or,

fixed-point arithmetic (lines i0—30)

decimal arithmetic

in the case of ZAP (zero and add) and CVB (convert to binary), by using the single argument  $k_2$  directly. CVD also involves a single argument only (i1).

convert (lines j0--55

The argument  $k_i$  is determined (j19) as the signed base-10 value of the vector  $\mathbf{\sigma}^1/\mathbf{v}$  of decimal digits,  $\mathbf{v}$  being assembled (j15) by catenating the base-2 values of half-bytes from field i. The last half-byte determines the sign (j19), a negative sign being represented by 13 (that is, 1101) in the extended BCD code ( $\mathbf{p}_{12} = 0$ ), and by 11 in the American Standard code. For example, if  $\mathbf{p}_{12} = 0$ ,  $\mathbf{l}_1 = 1$  and the bytes at  $\mathbf{M}^{a_1}$  and  $\mathbf{M}^{a_{1+1}}$  are 0101 0000 and 1001 1101, respectively, then  $\mathbf{v} = 5$ , 0, 9, 13, and  $\mathbf{k}_1 = -509$ .

The result k is converted to the decimal representation and stored (j34-42) and, except for DP (divide decimal), the operations end on line j43. Because of the setting of j on line j33, the quotient k is stored only in the first  $(l_1 + 1) - (l_2 + 1)$  bytes of the first field, leaving space of length  $(l_2 + 1)$  for the remainder, which is computed on line j47 and converted and stored by repeating from line j35.

CVD produces an 8-byte result (j2), and CVD and CVB produce specification exceptions (j39, 3) if the argument address is not at an 8-byte boundary. For MP and DP, a specification exception is occasioned (j9) if the length of the second field exceeds either 8 bytes or the length of the first (i.e., the result) field. All specification exceptions suppress the instruction; except for CVD, in which the result field remains unchanged, all other errors make the relevant result fields unreliable (j48–55). A data exception  $t_7$  occurs in ZAP (j8) if the fields overlap such that the right-hand end of the second field is to the right of the right-hand end of the first. Data exceptions caused by improper overlapping in the other instructions are detected and entered on line j18.

Two floating-point representations are used; the *short* (oneword) and long (two-word) representations utilize logical vectors  $\boldsymbol{u}$  of dimensions 32 and 64, respectively. A number n, represented by  $\boldsymbol{u}$ , is evaluated as follows:

```

u_0 is the sign (0 for +, and 1 for -);

\perp \overline{\alpha}^1/\alpha^8/u is the characteristic c;

2^{-\nu \overline{\alpha}^*/u} \times \perp \overline{\alpha}^8/u is the fraction f;

c - 64 is the exponent e; and

|n| is equal to f \times 16^c.

```

The program comprises three major segments, the fetching of operands u and v (lines k0-16), the computation of the results (k17-65), and the storing of results and the setting of the condition code and of (lost) significance ( $t_{14}$ ) and exponent underflow ( $t_{13}$ ) exceptions (k66-73).

Floating point register i is selected by the address  $2 \times i$ , and the relevant addresses (both  $\mathbf{a}_1$  and  $\mathbf{a}_2$  in the RR format) are therefore subject to a specification exception check (k1) which suppresses the instruction. Specification exceptions occasioned by MAC also suppress the instruction (k14).

floating-point arithmetic (lines k0—73) The behavior of the computation phase will be illustrated by AD (add normalized (long)). The argument with the smaller characteristic is shifted right (k21-23) by four times the difference in the characteristics, since the characteristic is taken to be the exponent of 16, and one hexadecimal digit comprises four bits.

The appropriate common characteristic determines j on line k24. Lines k28-30 show the determination of the arguments  $k_1$  and  $k_2$  as the signed values of the fractional parts of u and v, and the determination of the result k therefrom. The sign of the result is determined on line k32, and the fraction and possible fraction overflow i on line k33.

If fraction overflow occurs, line k37 shifts the fractional part of the result right one hexadecimal digit and prefixes it with hexadecimal 1 (thus restoring the overflow), and the next line increases the characteristic accordingly. If exponent overflow results (k39), the entire vector  $\boldsymbol{u}$  is questionable (k40); otherwise, the characteristic is specified by j on line k48. If fraction overflow does not occur, the program continues with line k41.

The treatment of a zero result fraction depends on the (lost) significance mask  $p_{39}$ ; if  $p_{39} = 1$ , the fraction is combined with the normal characteristic j (lines k41, 48); if  $p_{39} = 0$ , it is combined with a zero characteristic (i.e., the most negative possible exponent) and a positive sign (k42, 47).